# Cryogenic DAQs and FPGAs for Magnet Diagnostics

#### DIAGNOSTICS WORK GROUP MEETING #4

Marcos Turqueti

06/12/2020

# **LBNL** Activities

ATAP, Nuclear Sciences and Engineering

- Active Cryogenic Electronic Envelope (2013) U.S. Patent No. 10,240,875 (Supercon)

- Commercial off-the-shelf cryogenic components (4k-77k) ADCs, Amplifiers, Diodes, FPGAs, Laser Diodes, Optical Isolators, Voltage

Regulators, Transistors and Passives

- Field Programmable Gate Array (FPGA) on Cryogenic Environments (first board 2015)

- FPGA operating with COTS ADC (LTC2418)

- FPGA based ADC

- Cryogenic Magnetic Sensors Acoustic Sensors (Maxim) Electron Beam Sensor (LDRD)

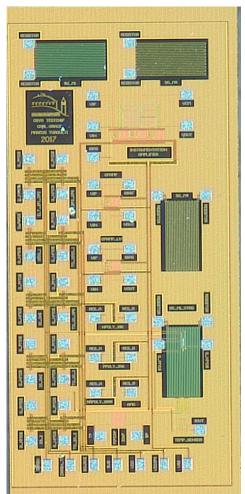

- 160nm Cryogenic ASIC (2018)

16 channels 12b 10MSPS ADC, 1 MSPS 10b ADC, Charge Amplifier, Voltage

Regulator, Strain Gauge, Sea-of-Transistors, Memory (C.Grace, D.Gnani)

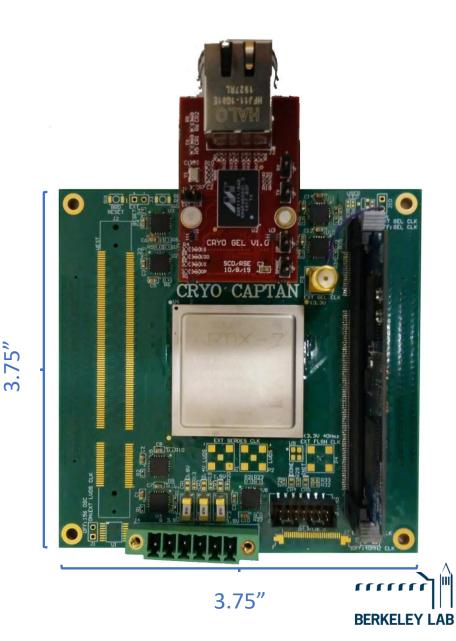

- 3<sup>th</sup> Gen FPGA Test Board (2018)

- 4<sup>th</sup> Gen FPGA/DAQ (2019-2020) LBNL Fermilab/CD

## Motivation

### Instrumentation of Cryogenic Experiments

- Data interface fully digital

- Simplification of cryostat feedthrough

- Noise reduction

- System simplification (no long analog cables present)

- Flexibility

- Cost reduction

- Increase time of oxide breakdown

## **Data Acquisition for Magnet Diagnostics**

- Strain Gauge

- Voltage Taps

- Temperature Sensor

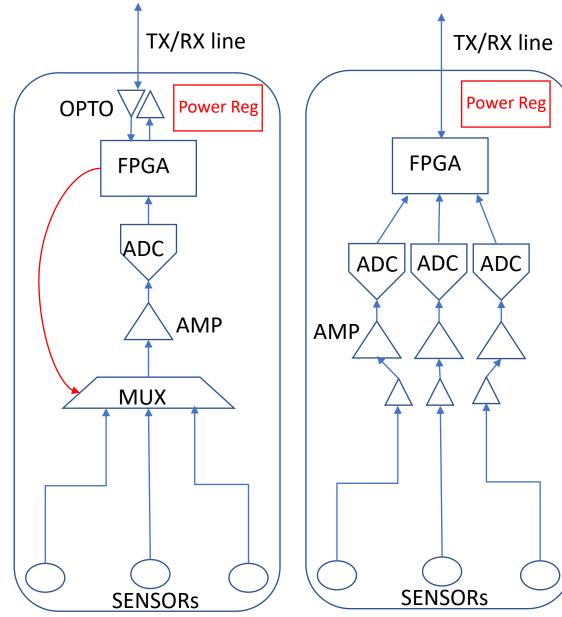

# Architectures for cryogenic DAQ

#### Power:

- Switched Capacitor+LDO

- Power over Fiber

- LED supply

#### **Communications:**

- JESD

- LVDS

- CMOS

- Ethernet (PHY?)

Over copper or fiber

Single or multiple lanes.

Typically one lane provides

300Mbps

#### Isolation:

Opto or capacitive

# **Bypassing the Problem**

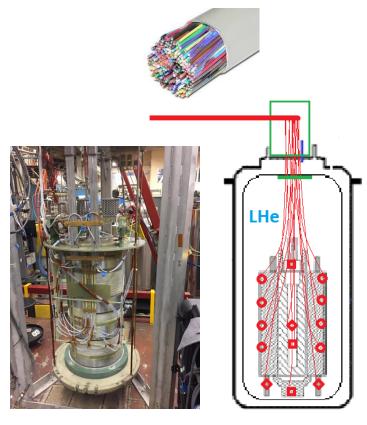

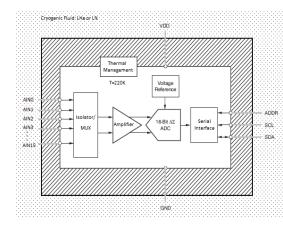

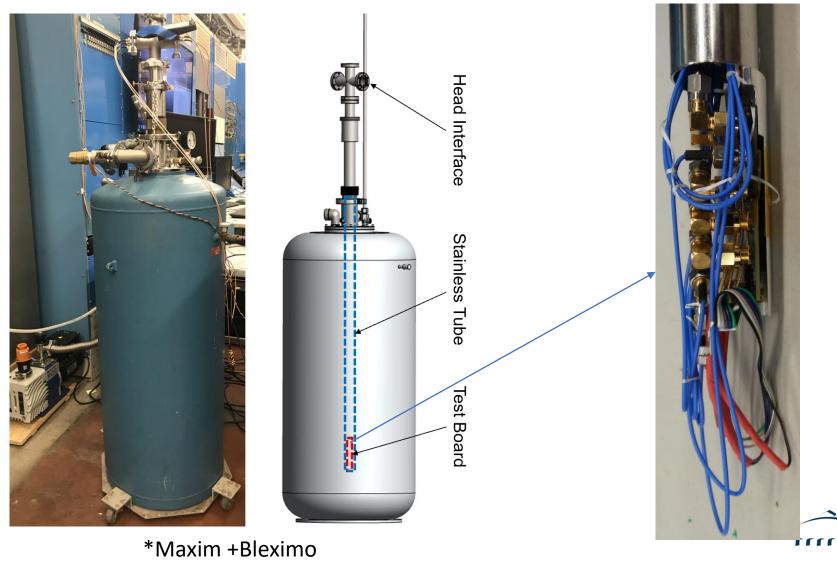

#### ACEe - Active Cryogenic Electronic Envelope (Gen 1)

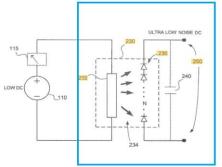

Alternative: Power Over Fiber

- For LHe Operation

- Internal Temperature (70k to 100k)

- 16 analog channels

- 3000V input multiplexed isolation

- 16 bit ADC providing 1 MSPS per channel

- Low noise ADC, SFDR >100dB

- 3 wires digital interface

- Automatic temperature control

- Internal voltage reference

- 250mW maximum power dissipation

- Non-magnetic components

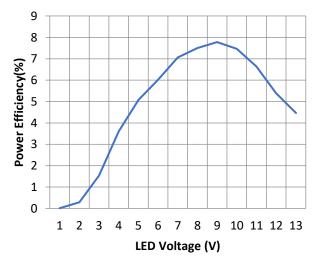

Electro-Optical Power Converter LED: AA1010SE28Zc 80nm shift at LHe

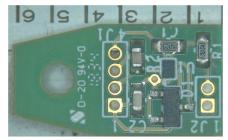

## Systems with COTS cryogenic components

#### LN Test

LHe Test

- ADCs

- 24b / 20kSPS

- 12b / 10MSPS

- 4b / 500MSPS

- Amplifiers (up to 500MHz)

- **Diodes** (HV protection 1A)

- **FPGAs** (28nm- 45nm)

- Laser Diodes Optical Isolators

- Voltage Regulators

- LDO and SW capacitor

- Transistors

- JFET

- HEMT

- MOSFET

- Passives

- Capacitors and resistors

Basic COTS component

Slow Amplifier (Acoustic Instrumentation)

Fast Amplifier -500MHz

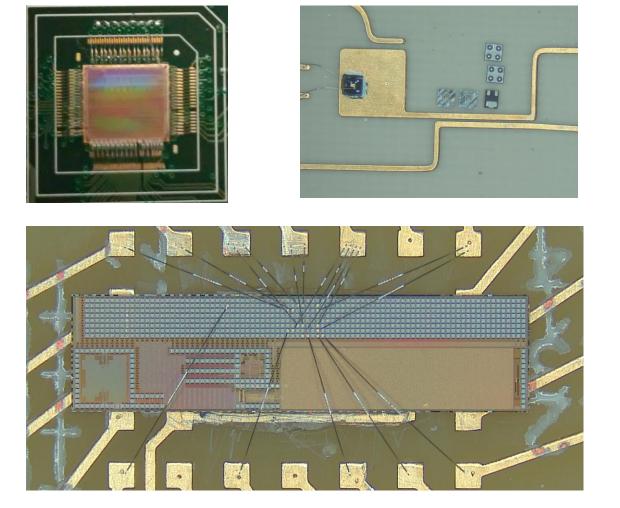

# **ASICs for Cryogenics**

\$\$!,Development time, Not Flexible Application Specific, Low Power

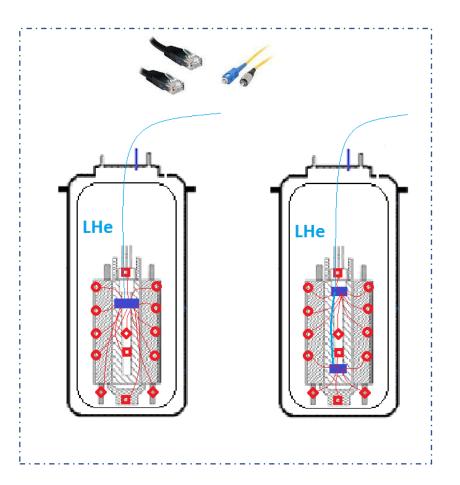

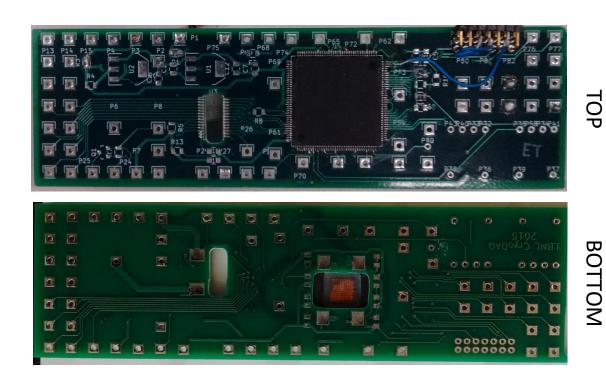

## CryoDAQ

- Current versions are capable of dealing with 32 analog channels

- Data is transmitted fully digital

- System resides inside the cryostat and is capable of operating at 4.2k

- Tests were already performed with strain gauges

- Two existing versions:

- Strain Gauge (SG) version: 20 SPS per channel

- Voltage Taps (VT) version: 200kSPS per channel

Leaded Part

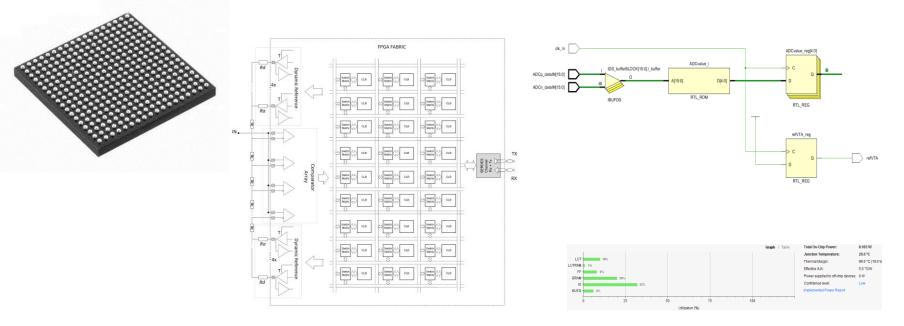

## FPGA Based n-bit Analog to Digital Converter

Reconfigurable Flash Folding Architecture. With this architecture it is possible to change the ADC resolution on the fly.

#### Test Setup at LBNL

BERKELEY LAB

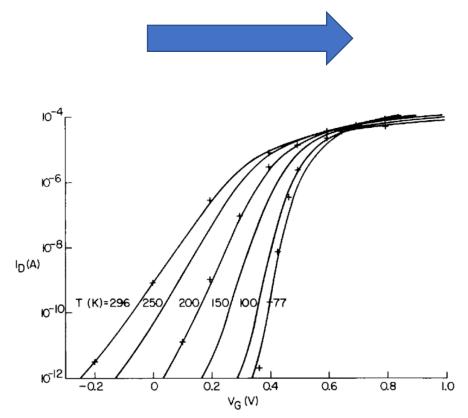

## Threshold (Vth)

For an n-channel enhancement mode MOS transistor, the formula for threshold voltage is

$$V_{\rm Th} = V_{\rm FB} + 2\phi_{\rm F} + \frac{\sqrt{2\varepsilon_0\varepsilon_{\rm s}qN_{\rm A}(2\phi_{\rm F} + V_{\rm SB})}}{C_{\rm ox}},$$

where  $V_{\rm FB}$  = flat-band voltage,  $\phi_{\rm F}$  = bulk potential,  $\varepsilon_0$  = free-space permittivity,  $\varepsilon_{\rm s}$  = dielectric constant of silicon, q = electronic charge,  $N_{\rm A}$  = acceptor doping concentration,  $V_{\rm SB}$  = substrate bias and  $C_{\rm ox}$  = oxide capacitance per unit area. Also,

$$V_{\rm FB} = \phi_{\rm ms} - \frac{Q_{\rm f}}{C_{\rm ox}} - \frac{1}{\varepsilon_0 \varepsilon_{\rm ox}} \int_0^{t_{\rm ox}} \rho_{\rm ox}(x) x dx,$$

where  $\phi_{\rm ms}$  is the metal-semiconductor work function,  $Q_{\rm f}$  is the fixed charge in the oxide,  $\varepsilon_{\rm ox}$  is the relative permittivity of silicon dioxide,  $\rho_{\rm ox}(x)$  is the charge density in an oxide of thickness  $t_{\rm ox}$  varying with distance x in the oxide. For an n-type polysilicon gate (STMicroelectronics 2006)

$$\phi_{\rm ms} = -\left(\frac{k_{\rm I}T}{q}\ln\left(\frac{N_{\rm D(g)}N_{\rm A}}{n_{\rm i}^2}\right),$$

### **Threshold Voltage**

**Fig. 16.** Subthreshold current of MOSFET as a function of temperature from 77 to 296 K. (After Gaensslen *et al.* [43].) (Parameters:  $L = 9 \ \mu m$ ;  $W = 87 \ \mu m$ ;  $V_d = 0.1 \ V$ ;  $V_{s-sub} = 0 \ V$ . Values, calculated by using two-dimensional model: +. Slope =  $(q/2.3 \ kT)[C_{ox}/(C_{ox} + C_{Si} + C_{FS})].)$

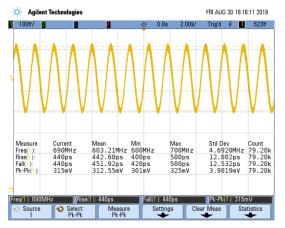

### Artix 7 – FPGA (~1x1 cm)

XC7A15T

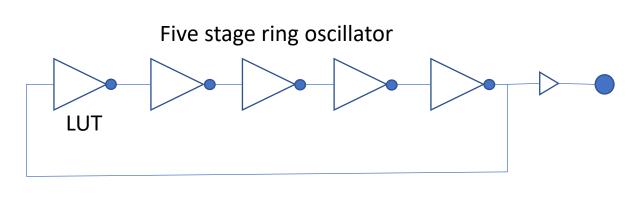

#### **Test Circuits**

VCCint = 2.1V VCCO = 2.8V VCCAUX = 2.8V

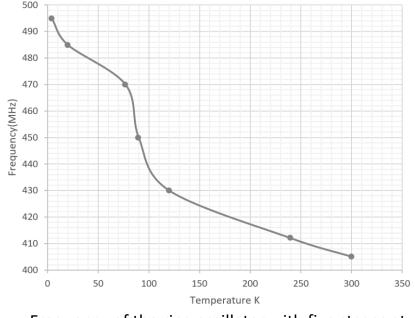

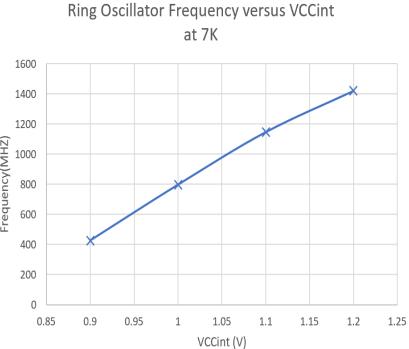

Frequency increase with temperature. Parasitic capacitance decreases

Frequency of the ring oscillator with five stages at different temperatures.

### Artix 7 – Seven stages ring oscillator

#### **FPGA Performance Highlights**

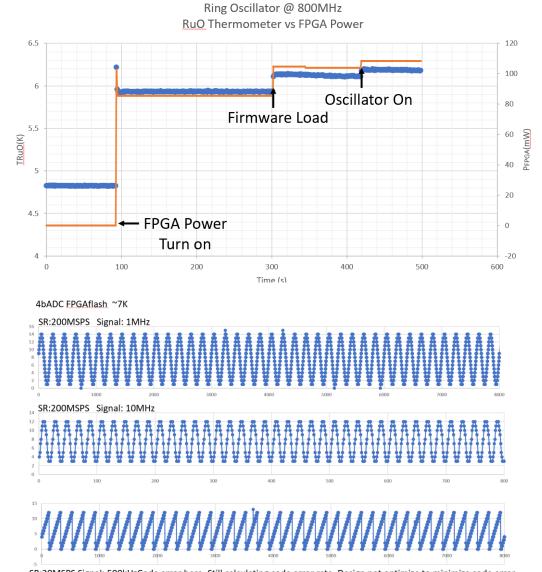

SR:20MSPS Signal: 500kHzCode error here. Still calculating code error rate. Design not optimize to minimize code error.

7.05

7

6.95 424

#### **FPGA Performance Highlights**

7.4 7.35 7.3 7.25 7.25 7.2 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.15 7.1

426

426.5

Ring Oscillator Temperature vs Frequency

425

Ring Oscillator Frequency(MHz)

424.5

425.5

#### **FPGA Performance Highlights**

- Operates at 4.2K reliably both in Liquid Helium and on cold finger (at ~4.2K). Over 28 thermal cycles and 700 hours cold (~4K). No degradation detected. Even when submitted to thermal shock (dipping in LN);

- 60 mW power consumption with 3 stage ring oscillator +XADC running at 400MHz;

- 150 mW power consumption with 3 stage ring oscillator +XADC running at 1000MHz;

- 550 mW power consumption with 3 stage ring oscillator +XADC running at 1400MHz (max achieved clock) LVCMOS 1.8;

- Most of the power (80% for the 1.4GHz) is dissipated at the IO driver with 50 Ohms termination, temperature at the FPGA went up to 10K;

- For the 4bit ADC at 200MSPS power consumption was 300mW with Chipscope in. Estimated to be around 140 mW without Chipscope;

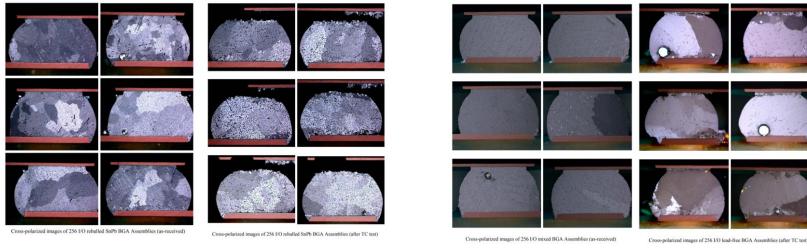

## **BGA Reliability**

Sn/Pb

Lead Free

\*TEMPERATURE CYCLING RELIABILITY OF REBALLED AND REWORKED BALL GRID ARRAY PACKAGES IN SNPB AND SAC ASSEMBLY Lei Nie, Doctor of Philosophy (Ph.D.), 2010

\*Indium balls are even better

## **BGA Reliability**

| Cycle Type                     | Number of<br>Cycles | Typical<br>Cooldown<br>Time(s) | Typical<br>Warmup<br>Time(s) | Total Number<br>of Hours<br>Cold(Hs) |

|--------------------------------|---------------------|--------------------------------|------------------------------|--------------------------------------|

| LN Submersion                  | 14                  | 5                              | 300                          | ~5                                   |

| LHe Submersion                 | 6                   | 7000                           | 200000                       | ~360                                 |

| LHe Cold Finger (290K to 4.2K) | 8                   | 3000                           | 170000                       | ~400                                 |

### Artix 7 Series

#### Artix-7 FPGA Product Table

|                          | XC7.    | A12T XC7A15T XC7 | A25T XC7A35T XC7 | A50T XC7A75T XC7 | XC7A200T |

|--------------------------|---------|------------------|------------------|------------------|----------|

| COMPARE COMPARE          | XC7A12T | XC7A15T          | XC7A25T          | XC7A35T          | хс7а50т  |

| Logic Cells              | 12,800  | 16,640           | 23,360           | 33,280           | 52,160   |

| DSP Slices               | 40      | 45               | 80               | 90               | 120      |

| Memory <mark>(kb)</mark> | 720     | 900              | 1,620            | 1,800            | 2,700    |

| GTP 6.6Gb/s Transceivers | 2       | 4                | 4                | 4                | 4        |

| I/O Pins                 | 150     | 250              | 150              | 250              | 250      |

#### Artix-7 FPGA Product Table

| COMPARE 🕻 🕻 Reset        | ХС7А35Т 🛛 | XC7A50T | XC7A75T 🛛 | XC7A100T | ХС7А200Т |  |

|--------------------------|-----------|---------|-----------|----------|----------|--|

| Logic Cells              | 33,280    | 52,160  | 75,520    | 101,440  | 215,360  |  |

| DSP Slices               | 90        | 120     | 180       | 240      | 740      |  |

| Memory <mark>(kb)</mark> | 1,800     | 2,700   | 3,780     | 4,860    | 13,140   |  |

| GTP 6.6Gb/s Transceivers | 4         | 4       | 8         | 8        | 16       |  |

| I/O Pins                 | 250       | 250     | 300       | 300      | 500      |  |

**BERKELEY L**

AB

## Implemented test structures

- LUT

- I/O (LVCMOS25 operating at 2.8V, 4mA)

- Ring Oscillator

- Counters (8/16 bits)

- Shift register (16 bits)

- LVDS tx/rx communications

- ADC

Evaluated at 290K,77K\*,4.2K\* \*immersed

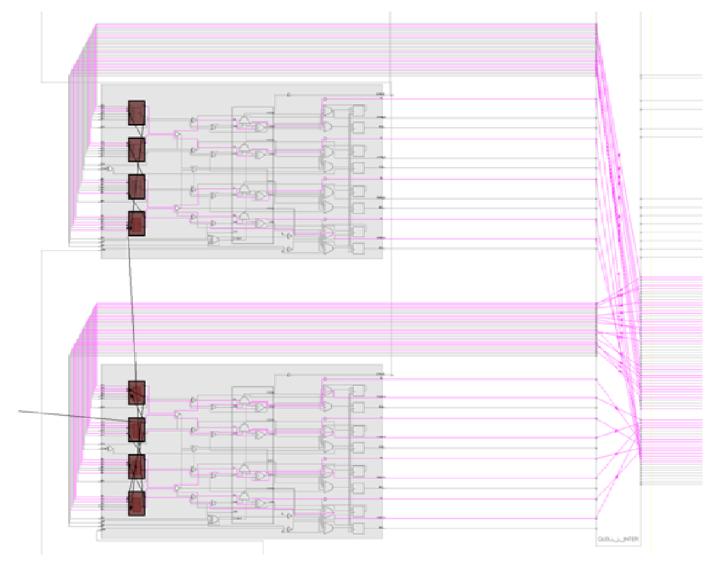

# Gen4 CryoDAQ – LBNL-Fermilab

- Large Artix FPGA (28nm)

- 64 Analog channels

- External Clock

- Laser Driver for communications

- LDO's

- External Clock

- Max operational clock 1GHz

- Expected around 1 W of power dissipation

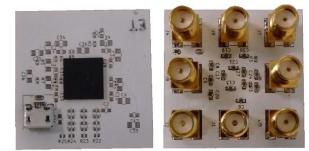

## ADC board

- 32 ADCs

- Sampling rate up to 100MSPS (50MHz signals)

- 14bits

- Not tested cold yet

### **Possible Issues**

- PLL, SERDES, iDelay, XADC (dedicated hardware)

- Asynchronous circuits timing uncertainty

- I/O threshold fluctuation

- Increased power consumption (+40% from room temp at 4.2K)

- Bump bond detachment with thermal cycles

- Difficult access (inside the cryostat)

- Power consumption

## Conclusions

- Many options available for cryogenic data acquisition

- COTS components can be used

- Growing number of Applications Specific Integrated Circuits (ASICs) available

- Software developed needed

- More collaboration needed between potential users

- Digital Magnet

- Ethernet PHY

- Materials SiGe, GaN ...

- Bump bond (Indium)

- Simulations/Characterization